# Lenovo

# Tuning UEFI Settings for Performance and Energy Efficiency on AMD Processor-Based ThinkSystem Servers

Last Update: June 2022

Covers the ThinkSystem SR635, SR645, SR655 and SR665 servers with AMD EPYC 7002 and 7003 processors Defines UEFI preset operating modes for Maximum Performance and Maximum Efficiency

Provides detailed information on key UEFI tuning parameter settings Explains AMD NUMA domains and tuning options and the Determinism Slider tuning parameter

John Encizo Kin Huang Joe Jakubowski Robert R. Wolford

# Abstract

Properly configuring UEFI parameters in a server is important for achieving a desired outcome such as maximum performance or maximum energy efficiency. This paper defines preset UEFI operating modes for Lenovo® ThinkSystem<sup>™</sup> servers running AMD EPYC 7002 and 7003 Series processors that are optimized for each of these outcomes. In addition, a thorough explanation is provided for each of the UEFI parameters so they can be fine-tuned for any particular customer deployment.

This paper is for customers and for business partners and sellers wishing to understand how to optimize UEFI parameters to achieve maximum performance or energy efficiency of Lenovo ThinkSystem servers with second-generation and third-generation AMD EPYC processors.

At Lenovo Press, we bring together experts to produce technical publications around topics of importance to you, providing information and best practices for using Lenovo products and solutions to solve IT challenges. See a list of our most recent publications:

http://lenovopress.com

# Contents

| Introduction                                          |

|-------------------------------------------------------|

| Summary of operating modes 3                          |

| UEFI menu items for SR635 and SR655 8                 |

| UEFI menu items for SR645 and SR665 24                |

| Hidden UEFI Items for SR645 and SR665 41              |

| Low Latency and Low Jitter UEFI parameter settings 42 |

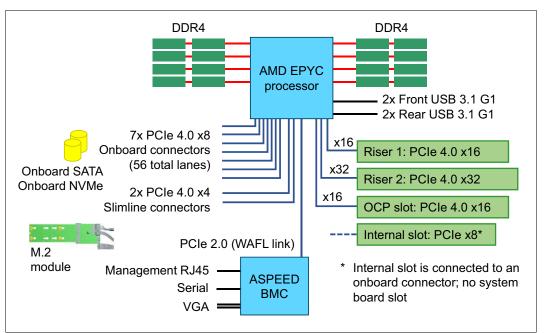

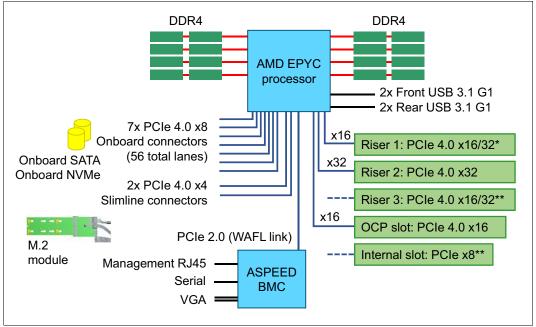

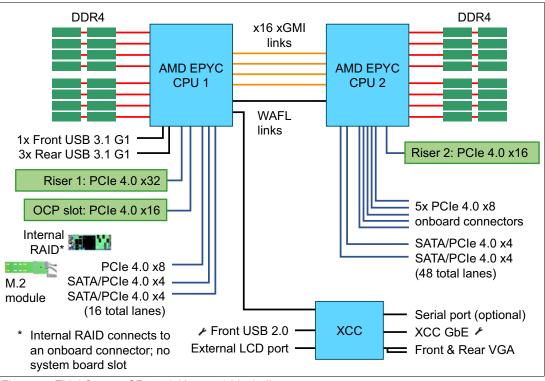

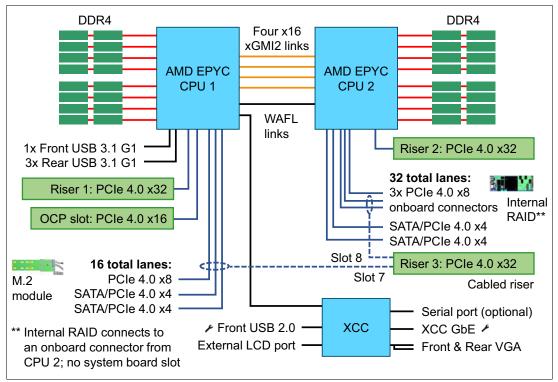

| ThinkSystem server platform design 45                 |

| References                                            |

| Change History                                        |

| Authors                                               |

| Notices                                               |

| Trademarks                                            |

# Introduction

The Lenovo ThinkSystem UEFI provides an interface to the server firmware that controls boot and runtime services. The system firmware contains numerous tuning parameters that can be set through the UEFI interface. These tuning parameters can affect all aspects of how the server functions and how well the server performs.

The Lenovo ThinkSystem SR635, SR645, SR655 and SR665 server UEFI contains operating modes that pre-define tuning parameters for maximum performance or maximum energy efficiency. This paper describes the tuning parameter settings for each operating mode and other tuning parameters to consider for performance and efficiency.

**AMD 1S and 2S differences:** The menu structure for 1-socket servers (SR635 and SR655) differs from 2-socket servers (SR645 and SR665). Some menu items between the two groups of servers may appear very similar but the location and associated Redfish, OneCLI and ASU variable can be subtly different.

# Summary of operating modes

The ThinkSystem SR635, SR655, SR645 and SR665 servers with 2nd and 3rd Gen AMD EPYC processors offer two preset operating modes, Maximum Efficiency and Maximum Performance. These modes are a collection of predefined low-level UEFI settings that simplify the task of tuning the server for either maximum performance or energy efficiency.

The two pre-defined modes are as follows:

- Maximum Efficiency (the default): Maximizes performance/watt efficiency while maintaining reasonable performance

- Maximum Performance: Achieves maximum performance at the expense of higher power consumption and lower energy efficiency

# Summary for SR635 and SR655 (1-socket servers)

Table 1 summarizes the settings that are made for each mode selected for the SR635 and SR655 servers.

The values in the Category column (column 3) in each table are as follows:

- Recommended: Settings follow Lenovo's best practices and should not be changed without sufficient justification.

- Suggested: Settings follow Lenovo's general recommendation for a majority of workloads but these settings can be changed if justified by workload specific testing.

- Test: The non-default values for the Test settings can optionally be evaluated because they are workload dependent.

| UEFI Setting       | Page | Category    | Maximum Efficiency | Maximum Performance |

|--------------------|------|-------------|--------------------|---------------------|

| Operating Mode     | 9    | Recommended | Maximum Efficiency | Maximum Performance |

| Determinism Slider | 10   | Recommended | Performance        | Power               |

| UEFI Setting                | Page | Category    | Maximum Efficiency                                                                 | Maximum Performance                                                                                                                                                                                                               |

|-----------------------------|------|-------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Performance Boost      | 10   | Recommended | Auto (Enabled)                                                                     | Auto (Enabled)                                                                                                                                                                                                                    |

| cTDP Control                | 11   | Recommended | Auto                                                                               | Manual and set cTDP to 300watt                                                                                                                                                                                                    |

| Memory Speed                | 12   | Recommended | 2933                                                                               | <ul> <li>3200 if highest memory<br/>bandwidth is required and<br/>if higher memory latency<br/>can be tolerated</li> <li>2933 if lower memory<br/>latency is required but<br/>with lower memory<br/>bandwidth vs. 3200</li> </ul> |

| L1 Stream HW Prefetcher     | 13   | Suggested   | Auto (Optionally experiment with Disable)                                          | Auto                                                                                                                                                                                                                              |

| L2 Stream HW Prefetcher     | 13   | Suggested   | Auto (Optionally experiment with Disable)                                          | Auto                                                                                                                                                                                                                              |

| Global C-state Control      | 13   | Recommended | Enabled                                                                            | Enabled                                                                                                                                                                                                                           |

| SMT Mode                    | 14   | Suggested   | Auto (Enabled)                                                                     | Auto (Enabled)                                                                                                                                                                                                                    |

| Package Power Limit         | 15   | Recommended | Auto                                                                               | 300watt                                                                                                                                                                                                                           |

| Memory Interleaving         | 15   | Recommended | Auto                                                                               | Auto                                                                                                                                                                                                                              |

| NUMA Nodes Per Socket       | 16   | Test        | NPS1 (Optionally experiment<br>with NPS=2 or NPS=4 for<br>NUMA optimized workloads | NPS1 (Optionally experiment<br>with NPS=2 or NPS=4 for<br>NUMA optimized workloads                                                                                                                                                |

| EfficiencyModeEn            | 17   | Recommended | Enabled                                                                            | Auto                                                                                                                                                                                                                              |

| Chipselect interleaving     | 17   | Recommended | Auto                                                                               | Auto                                                                                                                                                                                                                              |

| LLC as NUMA Node            | 17   | Test        | Auto                                                                               | Auto                                                                                                                                                                                                                              |

| SOC P-States                | 18   | Recommended | Auto                                                                               | Auto                                                                                                                                                                                                                              |

| P-State 1                   | 19   | Recommended | Enabled                                                                            | Enabled                                                                                                                                                                                                                           |

| P-State 2                   | 19   | Recommended | Enabled                                                                            | Enabled                                                                                                                                                                                                                           |

| DF C-states                 | 19   | Recommended | Enabled                                                                            | Enabled                                                                                                                                                                                                                           |

| Memory Power Down<br>Enable | 20   | Recommended | Enabled                                                                            | Enabled                                                                                                                                                                                                                           |

For the SR635 and SR655, Table 2 lists additional UEFI settings that you should consider for tuning for performance or energy efficiency. These setting are not part of the Maximum Efficiency and Maximum Performance modes.

Table 2 Other UEFI settings to consider for performance and efficiency for the SR635 and SR655

| Menu Item                         | Page | Category | Comments                                                                                                                               |

|-----------------------------------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| CPU Cores Activated<br>(Downcore) | 20   | Test     | This setting allows an administrator to power down some processor cores.                                                               |

| Preferred IO Bus                  | 21   | Test     | This setting provides some I/O performance benefit, however, you should perform tests on using your workload and evaluate the results. |

| Menu Item               | Page | Category | Comments                                                  |

|-------------------------|------|----------|-----------------------------------------------------------|

| L1 Stream HW Prefetcher | 22   | Test     | Optionally experiment with Disable for maximum efficiency |

| L2 Stream HW Prefetcher | 22   | Test     | Optionally experiment with Disable for maximum efficiency |

| L1 Stride Prefetcher    | 22   | Test     | Optionally experiment with Disable for maximum efficiency |

| L1 Region Prefetcher    | 22   | Test     | Optionally experiment with Disable for maximum efficiency |

| L2 Up/Down Prefetcher   | 22   | Test     | Optionally experiment with Disable for maximum efficiency |

# Summary for SR645 and SR665 (2-socket servers)

Table 3 summarizes the settings that are made for each mode selected for the SR645 and SR665. The values in the Category column (column 3) in each table are as follows:

- Recommended: Settings follow Lenovo's best practices and should not be changed without sufficient justification.

- Suggested: Settings follow Lenovo's general recommendation for a majority of workloads but these settings can be changed if justified by workload specific testing.

- Test: The non-default values for the Test settings can optionally be evaluated because they are workload dependent.

| Menu Item              | Page | Category    | Maximum Efficiency                                                                                                                                        | Maximum Performance                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Mode         | 24   | Recommended | Maximum Efficiency                                                                                                                                        | Maximum Performance                                                                                                                                                                                                                                                                                                                                                        |

| Determinism Slider     | 25   | Recommended | Performance                                                                                                                                               | Power                                                                                                                                                                                                                                                                                                                                                                      |

| Core Performance Boost | 26   | Recommended | Enable                                                                                                                                                    | Enable                                                                                                                                                                                                                                                                                                                                                                     |

| cTDP                   | 26   | Recommended | Auto                                                                                                                                                      | Maximum cTDP supported by the CPU                                                                                                                                                                                                                                                                                                                                          |

| Package Power Limit    | 27   | Recommended | Auto                                                                                                                                                      | Maximum cTDP supported by the CPU                                                                                                                                                                                                                                                                                                                                          |

| Memory Speed           | 28   | Recommended | 1 speed bin down from<br>maximum speed (for<br>example, if the maximum<br>speed is 3200 MHz, the<br>memory speed for this<br>selection will be 2933 MHz.) | Maximum<br>(For example with 2nd Gen<br>AMD EPYC processors, 3200<br>MHz if highest memory<br>bandwidth is required and if<br>higher memory latency can be<br>tolerated, or 2933 MHz if<br>lower memory latency is<br>required but with lower<br>memory bandwidth vs. 3200.<br>3200 MHz provides the<br>highest memory performance<br>with 3rd Gen AMD EPYC<br>processors) |

| Efficiency Mode        | 29   | Recommended | Enable                                                                                                                                                    | Disable                                                                                                                                                                                                                                                                                                                                                                    |

| 4-Link xGMI Max Speed  | 30   | Recommended | Minimum<br>The value is 10.667GT/s.                                                                                                                       | Maximum supported speed<br>(N). The value is 18GT/s for<br>SR645 and SR665.                                                                                                                                                                                                                                                                                                |

Table 3 UEFI Settings for Maximum Efficiency and Maximum Performance for SR645 and SR665

| Menu Item                            | Page | Category    | Maximum Efficiency                                                                 | Maximum Performance                                                                |

|--------------------------------------|------|-------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Global C-state Control               | 31   | Recommended | Enable                                                                             | Enable                                                                             |

| SOC P-states                         | 32   | Recommended | Auto                                                                               | Auto                                                                               |

| DF C-States                          | 32   | Recommended | Enable                                                                             | Enable                                                                             |

| P-State 1                            | 33   | Recommended | Enable                                                                             | Enable                                                                             |

| P-State 2                            | 33   | Recommended | Enable                                                                             | Enable                                                                             |

| Memory Power Down<br>Enable          | 34   | Recommended | Enable                                                                             | Enable                                                                             |

| NUMA Nodes per Socket                | 34   | Test        | NPS1 (Optionally experiment<br>with NPS=2 or NPS=4 for<br>NUMA optimized workloads | NPS1 (Optionally experiment<br>with NPS=2 or NPS=4 for<br>NUMA optimized workloads |

| Memory Interleave                    | 29   | Recommended | Auto                                                                               | Auto                                                                               |

| ACPI SRAT L3 Cache as<br>NUMA Domain | 38   | Test        | Disable                                                                            | Disable                                                                            |

For the SR645 and SR665, Table 4 lists additional UEFI settings that you should consider for tuning for performance or energy efficiency. These settings are not part of the Maximum Efficiency and Maximum Performance modes.

Table 4Other UEFI settings to consider for performance and efficiency for the SR645 and SR665

| Menu Item                        | Page | Category  | Comments                                                                                                                                             |

|----------------------------------|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMT Mode                         | 35   | Suggested | It is recommended to keep enabled as default.                                                                                                        |

| L1 Stream HW Prefetcher          | 36   | Suggested | Optionally experiment with Disable for maximum efficiency                                                                                            |

| L2 Stream HW Prefetcher          | 36   | Suggested | Optionally experiment with Disable for maximum efficiency                                                                                            |

| L1 Stride Prefetcher             | 36   | Test      | Optionally experiment with Disable for maximum efficiency                                                                                            |

| L1 Region Prefetcher             | 36   | Test      | Optionally experiment with Disable for maximum efficiency                                                                                            |

| L2 Up/Down Prefetcher            | 36   | Test      | Optionally experiment with Disable for maximum efficiency                                                                                            |

| Preferred IO Bus                 | 37   | Test      | This setting provides some I/O performance benefit, however, you should perform tests on using your workload and evaluate the results.               |

| xGMI Maximum Link Width          | 31   | Suggested | This setting is only available for the SR645 and SR665. Auto sets maximum width based on the system capabilities.                                    |

| PCIe Gen Speed Selection         | 38   | Suggested | Suggest keep Maximum                                                                                                                                 |

| CPPC                             | 39   | Suggested | Suggest keep Enable                                                                                                                                  |

| BoostFmax                        | 39   | Suggested | Suggest keep Auto                                                                                                                                    |

| DRAM Scrub Time                  | 40   | Suggested | Suggest keep 24 hour interval                                                                                                                        |

| Number of CPU Cores<br>Activated | 40   | Test      | This setting allows an administrator to power down some processor cores.                                                                             |

| PCIe Ten Bit Tag Support         | 42   | Test      | This setting enabled provides PCIe performance benefits. If the PCIe device doesn't have Ten Bit Tag support, it will cause issues, suggest disable. |

#### How to use OneCLI and Redfish to access these settings

In addition to using UEFI Setup, Lenovo also provides OneCLI/ASU variables and Redfish UEFI Setting Attribute names for managing system settings.

#### SR635 and SR655

The methods to use OneCLI/ASU variables and Redfish attributes in the SR635 and SR655 servers are as follows:

OneCLI/ASU variable usage

Show current setting:

Onecli config show "Bios.<Attribute>" --override --log 5 --imm <userid>:<password>@<IP Address>

Example:

onecli config show "Bios.Q00301\_Operating\_Mode" --override --log 5 --imm USERID:PASSWORD@10.240.55.226

Set a setting:

```

Onecli config set "Bios.<Attribute>" "<choice>" -override -log 5 -imm

<userid>:<password>@<IP Address>

```

Example:

```

onecli config set "Bios.Q00301_Operating_Mode" "Maximum_Efficiency" --override

--log 5 --imm USERID:PASSWORD@10.240.55.226

```

Redfish Attributes configure URL

Setting get URL: https://<BMC IP>/redfish/v1/Systems/Self/Bios

Setting set URL: https://<BMC IP>/redfish/v1/Systems/Self/Bios/SD

Example:

Get URL: https://10.240.55.226/redfish/v1/Systems/Self/Bios

Set URL: https://10.240.55.226/redfish/v1/Systems/Self/Bios/SD

Redfish Value Names of Attributes

If no special description, choice name is same as possible values. If there is a space character (' '), dash character ('-') or forward slash character ('/') in the possible values, replace them with underline ("\_"). This is because the Redfish standard doesn't support those special characters.

If you use OneCLI to configure the setting, OneCLI will automatically replace those characters with an underline character. However, if you use other Redfish tools, then you may need to replace them manually.

For example, "Operating Mode" has two choices: "Maximum Efficiency" and "Maximum Performance", their Redfish value names are Maximum\_Efficiency and Maximum\_Performance.

#### SR645 and SR665

The methods to use OneCLI/ASU variables and Redfish attributes in the SR645 and SR665 servers are as follows:

OneCLI/ASU variable usage

Show current setting:

Onecli config show "<OneCLI/ASU Var>" --override --log 5 --imm

<userid>:<password>@<IP Address>

Example:

onecli config show "OperatingModes.ChooseOperatingMode" --override --log 5

--imm USERID:PASSWORD@10.240.218.89

Set a setting:

Onecli config set "<OneCLI/ASU Var>" "<choice>" -override -log 5 -imm

<userid>:<password>@<IP Address>

Example:

onecli config set "OperatingModes.ChooseOperatingMode" "Maximum Efficiency"

--override --log 5 --imm USERID:PASSWORD@10.240.218.89

Redfish Attributes configure URL

Setting get URL: https://<BMC IP>/redfish/v1/Systems/1/Bios

Redfish Value Names of Attributes

If no special description, choice name is same as possible values. If there are space character (' '), dash line ('-') or slash line ('/') in the possible values, remove them. Because Redfish standard doesn't support those special characters.

If you use OneCLI to configure the setting, OneCLI will automatically remove them. But if you use other Redfish tools, then you may need to remove those characters by yourselves.

Example:

"Operating Mode" has three choices: "Maximum Efficiency", "Maximum Performance" and "Custom Mode", their Redfish value names are "MaximumEfficiency", "MaximumPerformance" and "CustomMode".

For more detailed information on the BIOS schema, please refer to the DMTF website:

https://redfish.dmtf.org/redfish/schema\_index

Usually, postman can be used for get/set BIOS schema:

https://www.getpostman.com/

The remaining sections in this paper provide details about each of these settings. We describe how to access the settings via System Setup (Press F1 during system boot).

# UEFI menu items for SR635 and SR655

The items below are exposed to server administrators in UEFI menus that can be accessed by pressing F1 when a server is rebooted, through the BMC service, or through command line utilities such as Lenovo's Advanced Settings Utility (ASU) or OneCLI. These parameters are exposed because they are commonly changed from their default values to fine tune server performance for a wide variety of customer use cases. Menu items described for the SR635 and SR655:

- "Operating Mode"

- "Determinism Slider"

- ► "Core Performance Boost" on page 10

- "cTDP Control" on page 11

- "Memory Speed" on page 12

- "Data Prefetchers" on page 13

- "Global C-State Control" on page 13

- "SMT Mode" on page 14

- "PPL (Package Power Limit)" on page 15

- "Memory Interleaving" on page 15

- "NUMA nodes per socket" on page 16

- "EfficiencyModeEn" on page 17

- "Chipselect Interleaving (Rank Interleaving)" on page 17

- "LLC as NUMA node" on page 17

- "SOC P-states" on page 18

- "P-State 1" on page 19

- ▶ "P-State 2" on page 19

- ▶ "DF (Data Fabric) C-States" on page 19

- "Memory Power Down Enable" on page 20

- "CPU Cores Activated (Downcore)" on page 20

- ▶ "Preferred IO Bus" on page 21

- ▶ "Data Prefetchers" on page 22

# **Operating Mode**

This setting is used to set multiple processor and memory variables at a macro level.

Choosing one of the predefined Operating Modes is a way to quickly set a multitude of processor and memory variables. It is less fine grained than individually tuning parameters but does allow for a simple "one-step" tuning method for two primary scenarios.

**Tip:** Prior to optimizing a workload for maximum performance, it is recommended to set the Operating Mode to "Maximum Performance" and then reboot rather than simply starting from the Maximum Efficiency default mode and then modifying individual UEFI parameters. If you don't do this, some settings may be unavailable for configuration.

This setting is accessed as follows:

- ► System setup: Main → Operating Modes → Operating Mode

- Redfish: Q00301\_Operating\_Mode

Possible values:

Maximum Efficiency (default)

Maximizes the performance / watt efficiency with a bias towards power savings.

Maximum Performance

Maximizes the absolute performance of the system without regard for power savings. Most power savings features are disabled and additional memory power / performance settings are exposed.

#### **Determinism Slider**

The determinism slider allows you to select between uniform performance across identically configured systems in you data center (by setting all servers to the Performance setting) or maximum performance of any individual system but with varying performance across the data center (by setting all servers to the Power setting).

When setting Determinism to Performance, ensure that cTDP and PPL are set to the same value (see "cTDP Control" on page 11 and "PPL (Package Power Limit)" on page 15 for more details). The default (Auto) setting for most processors will be Performance Determinism mode.

Determinism Slider should be set to Power for maximum performance and set to Performance for lower performance variability.

This setting is accessed as follows:

- System Setup:

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  Determinism Slider

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  Determinism Slider

- Redfish: Q00059\_Determinism\_Slider

Possible values:

Auto

Use the default determinism for the processor. For all EPYC 7002 and 7003 Series processors, the default is Performance.

Power

Ensure maximum performance levels for each CPU in a large population of identically configured CPUs by throttling CPUs only when they reach the same cTDP. Forces processors that are capable of running at the rated TDP to consume the TDP power (or higher).

Performance (default)

Ensure consistent performance levels across a large population of identically configured CPUs by throttling some CPUs to operate at a lower power level

#### **Core Performance Boost**

Core Performance Boost (CPB) is similar to Intel Turbo Boost Technology. CPB allows the processor to opportunistically increase a set of CPU cores higher than the CPU's rated base clock speed, based on the number of active cores, power and thermal headroom in a system.

Two levels of boosted P-states are supported.

- Compute units can be placed in the first level of boosted P-states if the processor power consumption remains within the TDP limit.

- The second level of boosted P-states can only be achieved if a subset of compute units are in CC6 low-power sleep state and the processor power consumption remains within the TDP limit.

When more than two physical CPU cores facilitating four hardware threads (2C4T) per die are active, the maximum CPU frequency achieved is hardware P0.

Consider using CPB when you have applications that can benefit from clock frequency enhancements. Avoid using this feature with latency-sensitive or clock frequency-sensitive applications, or if power draw is a concern. Some workloads do not need to be able to run at the maximum capable core frequency to achieve acceptable levels of performance.

To obtain better power efficiency, there is the option of setting a maximum core boost frequency. This setting does not allow you to set a fixed frequency. It only limits the maximum boost frequency. If the BoostFmax is set to something higher than the boost algorithms allow, the SoC will not go beyond the allowable frequency that the algorithms support.

This setting is accessed as follows:

- System setup:

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  Core Performance Boost

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  Core Performance Boost

- Redfish: Q00052\_Core\_Performance\_Boost

Possible values:

► Auto (default)

The Auto setting maps to enabling Core Performance Boost.

Disabled

Disables Core Performance Boost so the processor cannot opportunistically increase a set of CPU cores higher than the CPU's rated base clock speed.

# **cTDP** Control

Configurable Thermal Design Power (cTDP) allows you to modify the platform CPU cooling limit. A related setting, Package Power Limit (PPL), discussed in the next section, allows the user to modify the CPU Power Dissipation Limit.

Many platforms will configure cTDP to the maximum supported by the installed CPU. For example, an EPYC 7502 part has a default TDP of 180W but has a cTDP maximum of 200W. Most platforms also configure the PPL to the same value as the cTDP. Please refer to Table 9 on page 48 and Table 10 on page 49to get maximum cTDP of you installed processor.

If the Determinism slider parameter is set to Performance (see "Determinism Slider" on page 10), cTDP and PPL must be set to the same value, otherwise, the user can set PPL to a value lower than cTDP to reduce system operating power. The CPU will control CPU boost to keep socket power dissipation at or below the specified Package Power Limit.

For maximum performance, set cTDP and PPL to the maximum cTDP value supported by the CPU. For increased energy efficiency, set cTDP and PPL to Auto which sets both parameters to the CPU's default TDP value.

This setting is accessed as follows:

- System setup:

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  cTDP Control

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  cTDP Control

- Redfish: Q00060\_cTDP\_Control

Possible values:

- cTDP Control

- Manual

- Set customized configurable TDP

- Auto (default)

Use the platform and the default TDP for the installed processor.

- ▶ cTDP

- Set the configurable TDP (in Watts)

# **Memory Speed**

The memory speed setting determines the frequency at which the installed memory will run. Consider changing the memory speed setting if you are attempting to conserve power, since lowering the clock frequency to the installed memory will reduce overall power consumption of the DIMMs.

With the second-generation AMD EPYC processors, setting the memory speed to 3200 MHz results in higher memory bandwidth when compared to operation at 2933 MHz, but will also result in a higher memory latency. This higher latency is due to the memory bus clock and the memory/IO die clock not being synchronized when the memory speed is set to 3200 MHz. Customers should evaluate both memory speeds for their applications if supported by 2nd generation AMD EPYC 7002 processors.

With the third-generation AMD EPYC processors, setting the memory speed to 3200MHz does not result in higher memory latency when compared to operation at 2933 MHz. The highest memory performance is achieved when the memory speed is set to 3200 MHz and the memory DIMMs are capable of operating at 3200 MHz.

This setting is accessed as follows:

- System setup:

- Main  $\rightarrow$  Memory Speed

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  Memory Speed

- Redfish: Q00304\_Memory\_Speed

Possible values:

Auto

Max Performance sets the memory to the maximum allowed frequency as dictated by the type of CPU installed. Will support 3200 MHz operation with 1 DIMM Per Channel on 1-socket servers if 3200 MHz memory is installed and if the processor supports a 3200 MHz memory speed.

► 2933 MHz (default)

Redfish value name is Memory\_Speed\_2933\_MHz.

2666 MHz

Redfish value name is Memory\_Speed\_2666\_MHz.

▶ 2400 MHz

Redfish value name is Memory\_Speed\_2400\_MHz.

# **Data Prefetchers**

Most workloads will benefit from the L1 & L2 Stream Hardware prefetchers gathering data and keeping the core pipeline busy. By default, both prefetchers are enabled.

Application information access patterns, which tend to be relatively predictable, benefit greatly from prefetching. Most typical line-of-business, virtualization and scientific applications benefit from having pre-fetching enabled, however, there are however some workloads (for example, the SPECjbb 2015 Java application benchmark) that are very random in nature and will actually obtain better overall performance by disabling one or both of the prefetchers.

Further, the L1 and L2 stream hardware prefetchers can consume disproportionately more power vs. the gain in performance when enabled. Customers should therefore evaluate the benefit of prefetching vs. the non-linear increase in power if sensitive to energy consumption.

**Note:** L1 Stride Prefetcher, L1 Region Prefetcher and L2 Up/Down Prefetcher settings are only available for 3rd Gen EPYC processor.

This setting is accessed as follows:

- System Setup:

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  L1 Stream HW Prefetcher

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  L2 Stream HW Prefetcher

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  L1 Stream HW Prefetcher

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  L2 Stream HW Prefetcher

- ► Redfish:

- Q00054 L1 Stream HW Prefetcher

- Q00055\_L2\_Stream\_HW\_Prefetcher

Possible values:

Disabled

Disable L1/L2 Stream HW Prefetcher

Enabled

Enable L1/L2 Stream HW Prefetcher

Auto (default)

Maps to Enabled, enable the prefetcher.

#### Global C-State Control

C-states are idle power saving states. This setting enables and disables C-states on the server across all cores. When disabled, the CPU cores can only be in C0 (active) or C1 state. C1 state can never be disabled. A CPU core will be in the C1 state if the core is halted by the operating system.

Lenovo generally recommends that Global C-State Control remain enabled, however consider disabling it for low-jitter use cases.

This setting is accessed as follows:

- System setup:

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  Global C-State Control

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  Global C-State Control

- Redfish: Q00056\_Global\_C\_state\_Control

Possible values:

Disabled

I/O based C-state generation and Data Fabric (DF) C-states are disabled.

Enabled (default)

I/O based C-state generation and DF C-states are enabled.

Auto

Map to Enabled.

# SMT Mode

Simultaneous multithreading (SMT) is similar to Intel Hyper-Threading Technology, the capability of a single core to execute multiple threads simultaneously. An OS will register an SMT-thread as a logical CPU and attempt to schedule instruction threads accordingly. All processor cache within a Core Complex (CCX) is shared between the physical core and its corresponding SMT-thread.

In general, enabling SMT benefits the performance of most applications. Certain operating systems and hypervisors, such as VMware ESXi, can schedule instructions such that both threads execute on the same core. SMT takes advantage of out-of-order execution, deeper execution pipelines and improved memory bandwidth in today's processors to be an effective way of getting all of the benefits of additional logical CPUs without having to supply the power necessary to drive another physical core.

Start with SMT enabled since SMT generally benefits the performance of most applications, however, consider disabling SMT in the following scenarios:

- Some workloads, including many HPC workloads, observe a performance neutral or even performance negative result when SMT is enabled.

- Using multiple execution threads per core requires resource sharing and is a possible source of inconsistent system response. So disabling SMT could give benefit on some low-jitter use case.

- Some application license fees are based on the number of hardware threads enabled, not just the number of physical cores present. For this reason, disabling SMT on your EPYC 7002 and 7003 Series processor may be desirable to reduce license fees.

- Some older operating systems that have not enabled support for the x2APIC within the EPYC 7002 and 7003 Series processor, which is required to support beyond 255 threads. If you are running an operating system that does not support AMD's x2APIC implementation, and have two 64-core processors installed, you will need to disable SMT.

Operating systems such as Windows Server 2012 and Windows Server 2016 do not support x2APIC. Please refer to the following article for details:

https://support.microsoft.com/en-in/help/4514607/windows-server-support-and-ins tallation-instructions-for-amd-rome-proc This setting is accessed as follows:

- System setup:

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  SMT Mode

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  SMT Mode

- Redfish: Q00051\_SMT\_Mode

Possible values:

Auto (default)

Enables simultaneous multithreading

Disabled

Disables simultaneous multithreading so that only one thread or CPU instruction stream is run on a physical CPU core

# **PPL (Package Power Limit)**

The parameter sets the CPU package power limit. The maximum value allowed for PPL is the cTDP limit. Set PPL to the cTDP Maximum value when maximum performance is desired. PPL can be set to the cTDPminimum value or lower but reaching the set value of PPL is not guaranteed when it is set to less than cTDPminimum.

This setting is accessed as follows:

- ► System setup: Main → Operating Modes → Package Power Limit Control

- Redfish: Q00305\_Package\_Power\_Limit\_Control

Possible values:

Manual

If a manual value entered that is larger than the maximum value allowed (cTDP Maximum), the value will be internally limited to maximum allowable value.

► Auto (default)

Set to maximum value allowed by installed CPU

# **Memory Interleaving**

This setting allows interleaved memory accesses across multiple memory channels in each socket, providing higher memory bandwidth. Interleaving generally improves memory performance so the Auto (default) setting is recommended.

This setting is accessed as follows:

- System Setup:

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  Memory Interleaving

- Advanced  $\rightarrow$  Memory Configuration  $\rightarrow$  Memory Interleaving

- Redfish: Q00081\_Memory\_interleaving

Possible values:

Disabled

No interleaving

Auto (default)

Interleaving is automatically enabled if memory DIMM configuration supports it.

#### NUMA nodes per socket

This setting lets you specify the number of desired NUMA nodes per socket. NPS0 will attempt to interleave two sockets together into one NUMA node. NPS0 is not supported on the SR635 and SR655 one-socket servers.

Second and third-generation AMD EPYC processors support a varying number of NUMA Nodes per Socket depending on the internal NUMA topology of the processor. In one-socket servers, the number of NUMA Nodes per socket can be 1, 2 or 4 though not all values are supported by every processor. See Table 7 on page 47 and Table 8 on page 48 for the NUMA nodes per socket options available for each processor.

Applications that are highly NUMA optimized can improve performance by setting the number of NUMA Nodes per Socket to a supported value greater than 1.

This setting is accessed as follows:

- ► System Setup: Main → Operating Modes → NUMA nodes per socket

- Redfish: Q00302\_NUMA\_nodes\_per\_socket

Possible values:

Auto

One NUMA node per socket, NPS1.

- NPS4

- Four NUMA nodes per socket, one per Quadrant.

- Requires symmetrical Core Cache Die (CCD) configuration across Quadrants of the SoC.

- Preferred Interleaving: 2-channel interleaving using channels from each quadrant.

- NPS2

- Two NUMA nodes per socket, one per Left/Right Half of the SoC.

- Requires symmetrical CCD configuration across left/right halves of the SoC.

- Preferred Interleaving: 4-channel interleaving using channels from each half.

- NPS1 (default)

- One NUMA node per socket.

- Available for any CCD configuration in the SoC.

- Preferred Interleaving: 8-channel interleaving using all channels in the socket.

# **EfficiencyModeEn**

This setting enables an energy efficient mode of operation internal to the AMD EPYC Gen 2 and Gen 3 processors at the expense of performance. The setting should be enabled when energy efficient operation is desired from the processor. If desired, set it to Auto which disables the feature when maximum performance is desired.

This setting is accessed as follows:

- ► System Setup: Main → Operating Modes → EfficiencyModeEn

- Redfish: Q00303\_EfficiencyModeEn

Possible values:

Auto

Use performance optimized CCLK DPM settings

Enabled (default)

Use power efficiency optimized CCLK DPM settings

#### Chipselect Interleaving (Rank Interleaving)

This setting specifies if the system should use a DRAM rank also known as chipselect interleaving. This feature will spread memory accesses across the ranks of memory within a memory channel and will increase memory block access performance.

This feature requires the following memory configuration:

- Populated DIMMs have same rank size and type. Strongly recommend you populate DIMMs which have same part number.

- Number of ranks is a power of two.

This setting is accessed as follows:

- System Setup:

- Main  $\rightarrow$  Operating Modes  $\rightarrow$  Chipselect Interleaving

- Advanced  $\rightarrow$  Memory Configuration  $\rightarrow$  Chipselect Interleaving

- Redfish: Q00083\_Chipselect\_interleaving

Possible values:

Disabled

No interleaving. When your application data access is random, and very sensitive about latency, then you may disable it.

Auto (default)

Interleaving across the ranks within the memory channel.

#### LLC as NUMA node

Specifies whether the processor last-level caches (LLCs) are exposed to the operating system as NUMA nodes.

In certain server applications where workloads are managed by a remote job scheduler, it is desirable to pin execution to a single NUMA node, and preferably to share a single L3 cache

within that node. Hence BIOS Setup should support an L3AsNumaNode (Boolean) option to create a NUMA node for each Core Complex (CCX) L3 Cache in the system.

When enabled, this setting can improve performance for highly NUMA optimized workloads if workloads or components of workloads can be pinned to cores in a CCX and if they can benefit from sharing an L3 cache.

This setting is accessed as follows:

- ► System Setup: Main → Operating Modes → LCC as NUMA Node

- Redfish: Q00308\_LCC\_as\_NUMA\_Node

Possible values:

Disabled

LLCs are not exposed to the operating system as NUMA nodes.

Enabled

LLCs are exposed to the operating system as NUMA nodes.

Auto (default)

Maps to Disable where the LLCs are not exposed to the operating system as NUMA nodes.

#### SOC P-states

Infinity Fabric is a proprietary AMD bus that connects all the Core Cache Dies (CCDs) to the IO die inside the CPU as shown in Figure 5 on page 47. SOC P-states is the Infinity Fabric (Uncore) Power States setting. When Auto is selected the CPU SOC P-states will be dynamically adjusted. That is, their frequency will dynamically change based on the workload. Selecting P0, P1, P2, or P3 forces the SOC to a specific P-state frequency.

SOC P-states functions cooperatively with the Algorithm Performance Boost (APB) which allows the Infinity Fabric to select between a full-power and low-power fabric clock and memory clock based on fabric and memory usage. Latency sensitive traffic may be impacted by the transition from low power to full power. Setting APBDIS to 1 (to disable APB) and SOC P-states=0 sets the Infinity Fabric and memory controllers into full-power mode. This will eliminate the added latency and jitter caused by the fabric power transitions.

The following examples illustrate how SOC P-states and APBDIS function together:

- If SOC P-states=Auto then APBDIS=0 will be automatically set. The Infinity Fabric can select between a full-power and low-power fabric clock and memory clock based on fabric and memory usage.

- If SOC-P-states=<P0, P1, P2, P3> then APBDIS=1 will be automatically set. The Infinity Fabric and memory controllers are set in full-power mode.

- If SOC P-states=P0 which results in APBDIS=1, the Infinity Fabric and memory controllers are set in full-power mode. This results in the highest performing Infinity Fabric P-state with the lowest latency jitter.

This setting is accessed as follows:

- ► System setup: Main → Operating Modes → SOC P-states

- Redfish: Q00311\_SOC\_P\_states

Possible values:

► Auto (default)

When Auto is selected the CPU SOC P-states (uncore P-states) will be dynamically adjusted.

- ► **P0**: Highest-performing Infinity Fabric P-state

- ▶ P1: Next-highest-performing Infinity Fabric P-state

- ▶ P2: Next next-highest-performing Infinity Fabric P-state

- ► P3: Minimum Infinity Fabric power P-state

## P-State 1

This setting enables or disable the CPU's P1 operating state.

This setting is accessed as follows:

- ► System setup: Main → Operating Modes → P-State 1

- Redfish: Q00313\_P\_State\_1

Possible values:

- Enabled (default)

Enables CPU P1 P-state.

- Disabled

Disable CPU P1 P-state

# P-State 2

This setting enables or disable the CPU's P2 operating state.

This setting is accessed as follows:

- ► System setup: Main → Operating Modes → P-State 2

- Redfish: Q00314\_P\_State\_2

Possible values:

Enabled (default)

Enables CPU P2 P-state.

Disabled

Disable CPU P2 P-state.

# **DF (Data Fabric) C-States**

Much like CPU cores, the Infinity Fabric can go into lower power states while idle. However, there will be a delay changing back to full-power mode causing some latency jitter. In a low latency workload, or one with bursty I/O, one could disable this feature to achieve more performance with the tradeoff of higher power consumption.

This setting is accessed as follows:

► System setup: Main → Operating Modes → DF C-states

Redfish: Q00312\_DF\_C\_states

Possible values:

Enabled (default)

Enables Data Fabric C-states. Data Fabric C-states may be entered when all cores are in CC6.

Disabled

Disable Data Fabric (DF) C-states

#### **Memory Power Down Enable**

Low-power feature for DIMMs. Lenovo generally recommends that Memory Power Down remain enabled, however consider disabling it for low-latency use cases.

This setting is accessed as follows:

- System setup:

- System Settings  $\rightarrow$  Operating Modes  $\rightarrow$  Memory Power Down Enable

- System Settings  $\rightarrow$  Memory  $\rightarrow$  Memory Power Down Enable

- Redfish: Q00310\_Memory\_Power\_Down\_Enable

Possible values:

Enabled (default)

Enables low-power features for DIMMs.

Disabled

# **CPU Cores Activated (Downcore)**

UEFI allows the administrator to shut down cores in a server. This setting powers off a set number of cores for each processor in a system. As opposed to restricting the number of logical processors an OS will run on, this setting directly affects the number of cores powered on by turning off the core level power gates on each processor.

Manipulating the number of physically powered cores is primarily used in three scenarios:

- Where users have a licensing model that supports a certain number of active cores in a system

- Where users have poorly threaded applications but require the additional LLC available to additional processors, but not the core overhead

- ► Where users are looking to limit the number of active cores in an attempt to reclaim power and thermal overhead to increase the probability of Performance Boost being engaged.

This setting is accessed as follows:

- ► System Setup: Advanced → CPU Configuration → CPU Cores Activated

- Redfish: Q00053\_CPU\_Cores\_Activated

Possible values:

Auto (default):

Enable all cores

#### ► 2 Cores Per Die:

Enable 2 cores for each Core Cache Die. Redfish value name is CPU\_Cores\_Activated\_2\_Cores\_Per\_Die.

4 Cores Per Die:

Enable 4 cores for each Core Cache Die. Redfish value name is CPU\_Cores\_Activated\_4\_Cores\_Per\_Die.

#### ► 6 Cores Per Die:

Enable 6 cores for each Core Cache Die. Redfish value name is CPU\_Cores\_Activated\_6\_Cores\_Per\_Die.

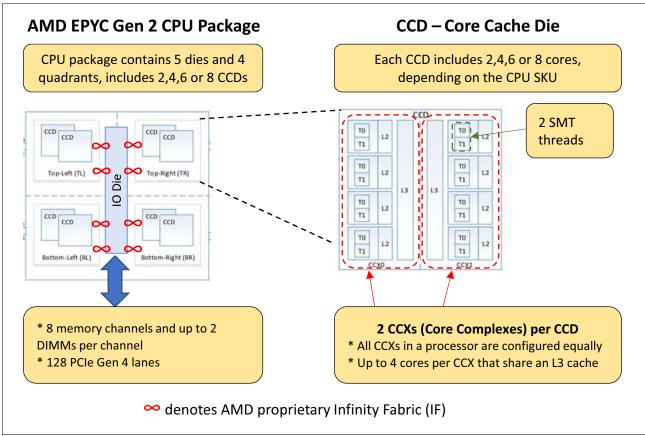

AMD EPYC Gen 2 and Gen 3 processors have a multi-die topology consisting of two or more Core Cache Die (CCD). Each CCD contains processor cores plus Level 2 and Level 3 caches. See Figure 5 on page 47 and Table 7 on page 47 and Table 8 on page 48 for more information on CCDs.

# **Preferred IO Bus**

AMD Preferred I/O complements Relaxed Ordering (RO) and ID-Based Ordering (IDO), rather than replace them. As with most performance tuning options, your exact workload may not perform better with Preferred I/O enabled but rather with RO or IDO. Lenovo recommends that you test your workload under all scenarios to find the most efficient setting.

If your PCIe device supports IDO or RO, and it is enabled, you can try enabling Preferred IO to determine whether your specific use case realizes an additional performance improvement. If the device does not support either of those features for your high bandwidth adapter, you can experiment with the Preferred IO mode capability available on the EPYC 7002 and 7003 Series processors. This setting allows devices on a single PCIe bus to obtain improved DMA write performance.

Note: The Preferred I/O can be enabled for only a single PCIe root complex (RC) and will affect all PCIe endpoints behind that RC. This setting gives priority to the I/O devices attached to the PCIe slot(s) associated with the enabled RC for I/O transactions.

This setting is accessed as follows:

- System Setup:

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  Preferred IO Bus

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  Preferred I/O Bus Number

- Redfish:

- Q00309 Preferred IO Bus

- Q00307 Preferred I O Bus Number

Possible values for Preferred IO Bus:

No Priority (default):

All PCIe buses have equal priority. Use this setting unless you have an I/O device, such as a RAID controller or network adapter, that has a clear need to be prioritized over all other I/O devices installed in the server.

Preferred

Enter a preferred I/O bus number in the range 00h-FFh to setup item "Preferred I/O Device Bus Number" to specify the bus number for which device(s) you wish to enable preferred I/O.

# **Data Prefetchers**

- L1 Stream Prefetcher: Uses history of memory access patterns to fetch next line into the L1 cache when cached lines are resued within a certain time period or access sequentially.

- L1 Stride Prefetcher: Uses memory access history to fetch additional data lines into L1 cache when each access is a constant distance from previous.

- L1 Region Prefetcher: Uses memory access history to fetche additional data line into L1 cache when the data access for a given instruction tends to be followed by a consistent pattern of subsequent access

- L2 Stream Prefetcher: Uses history of memory access patterns to fetch next line into the L1 cache when cached lines are resued within a certain time period or access sequentially.

- L2 Up/Down Prefetcher: Uses memory access history to determine whether to fetch the next or previous line for all memory accesses.

These fetchers use memory access history to determine whether to fetch the text or previous line for all memory access. Most workloads will benefit from these prefetchers gathering data and keeping the core pipeline busy. By default, these prefetchers all are enabled.

Application information access patterns, which tend to be relatively predictable, benefit greatly from prefetching. Most typical line-of-business, virtualization and scientific applications benefit from having pre-fetching enabled, however, there are however some workloads (for example, the SPECjbb 2015 Java application benchmark) that are very random in nature and will actually obtain better overall performance by disabling some of the prefetchers.

Further, the L1 and L2 stream hardware prefetchers can consume disproportionately more power vs. the gain in performance when enabled. Customers should therefore evaluate the benefit of prefetching vs. the non-linear increase in power if sensitive to energy consumption.

**Note:** L1 Stride Prefetcher, L1 Region Prefetcher and L2 Up/Down Prefetcher settings are only available for 3rd Gen EPYC processor.

This setting is accessed as follows:

- System setup:

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  L1 Stream HW Prefetcher

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  L2 Stream HW Prefetcher

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  L1 Stride Prefetcher

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  L1 Region Prefetcher

- Advanced  $\rightarrow$  CPU Configuration  $\rightarrow$  L2 Up/Down Prefetcher

- Redfish:

- Q00054\_L1\_Stream\_HW\_Prefetcher

- Q00055 L2 Stream HW Prefetcher

- Q00066\_L1\_Stride\_Prefetcher

- Q00067\_L1\_Region\_Prefetcher

- Q00068 L2 Up Down Prefetcher

Possible values:

- ► Auto (default)

- Maps to Enabled

Disabled

Disable corresponding Prefetcher

► Enabled

Enable corresponding Prefetcher

# UEFI menu items for SR645 and SR665

Below items are exposed to server administrators in UEFI menus that can be accessed by pressing F1 when a server is rebooted, through the XClarity Controller (XCC) service processor, or through command line utilities such as Lenovo's Advanced Settings Utility (ASU) or OneCLI. These parameters are exposed because they are commonly changed from their default values to fine tune server performance for a wide variety of customer use cases.

Menu items described for the SR645 and SR665:

- "Operating Mode"

- "Determinism Slider"

- "Core Performance Boost" on page 26

- "cTDP (Configurable TDP)" on page 26

- "PPL (Package Power Limit)" on page 27

- "Memory Speed" on page 28

- "Memory Interleave" on page 29

- "Efficiency Mode" on page 29

- "xGMI settings" on page 30

- "Global C-State Control" on page 31

- "SOC P-states" on page 32

- "DF (Data Fabric) C-States" on page 32

- "P-State 1" on page 33

- ▶ "P-State 2" on page 33

- "Memory Power Down Enable" on page 34

- "NUMA nodes per socket" on page 34

- ▶ "SMT Mode" on page 35

- "Data Prefetchers" on page 36

- "Preferred IO bus" on page 37

- ► "ACPI SRAT L3 Cache as NUMA Domain" on page 38

- ▶ "PCIe (PCI Express) Gen Speed Selection" on page 38

- "CPPC" on page 39

- ► "BoostFmax" on page 39

- "DRAM Scrub Time" on page 40

- "Number of CPU Cores Activated (Downcore)" on page 40

#### **Operating Mode**

This setting is used to set multiple processor and memory variables at a macro level.

Choosing one of the predefined Operating Modes is a way to quickly set a multitude of processor, memory, and miscellaneous variables. It is less fine grained than individually tuning parameters but does allow for a simple "one-step" tuning method for two primary scenarios.

**Tip:** Prior to optimizing a workload for maximum performance, it is recommended to set the Operating Mode to "Maximum Performance" and then reboot rather than simply starting from the Maximum Efficiency default mode and then modifying individual UEFI parameters. If you don't do this, some settings may be unavailable for configuration.

This setting is accessed as follows:

- ► System setup: System Settings → Operating Modes → Choose Operating Mode

- OneCLI/ASU variable: OperatingModes.ChooseOperatingMode

Redfish: OperatingModes ChooseOperatingMode

#### Default Setting: Maximum Efficiency

Possible values:

#### Maximum Efficiency

Maximizes the performance / watt efficiency with a bias towards power savings.

#### Maximum Performance

Maximizes the absolute performance of the system without regard for power savings. Most power savings features are disabled, and additional memory power / performance settings are exposed.

#### Custom Mode

Allow user to customize the performance settings. Custom Mode will inherit the UEFI settings from the previous preset operating mode. For example, if the previous operating mode was the Maximum Performance operating mode and then Custom Mode was selected, all the settings from the Maximum Performance operating mode will be inherited.

# **Determinism Slider**

The determinism slider allows you to select between uniform performance across identically configured systems in you data center (by setting all servers to the Performance setting) or maximum performance of any individual system but with varying performance across the data center (by setting all servers to the Power setting).

When setting Determinism to Performance, ensure that cTDP and PPL are set to the same value (see Configurable TDP control and PPL (Package Power Limit) for more details). The default (Auto) setting for most processors will be Performance Determinism mode.

Determinism Slider should be set to Power for maximum performance and set to Performance for lower performance variability.

This setting is accessed as follows:

- System setup:

- System Settings  $\rightarrow$  Operating Modes  $\rightarrow$  Determinism Slider

- System Settings  $\rightarrow$  Processors  $\rightarrow$  Determinism Slider

- OneCLI/ASU variable: Processors.DeterminismSlider

- Redfish: Processors\_DeterminismSlider

Possible values:

Power

Ensure maximum performance levels for each CPU in a large population of identically configured CPUs by throttling CPUs only when they reach the same cTDP. Forces processors that are capable of running at the rated TDP to consume the TDP power (or higher).

Performance (default)

Ensure consistent performance levels across a large population of identically configured CPUs by throttling some CPUs to operate at a lower power level

## **Core Performance Boost**

Core Performance Boost (CPB) is similar to Intel Turbo Boost Technology. CPB allows the processor to opportunistically increase a set of CPU cores higher than the CPU's rated base clock speed, based on the number of active cores, power and thermal headroom in a system.

Two levels of boosted P-states are supported.

- Compute units can be placed in the first level of boosted P-states if the processor power consumption remains within the TDP limit.

- The second level of boosted P-states can only be achieved if a subset of compute units are in CC6 state and the processor power consumption remains within the TDP limit.

When more than two physical CPU cores facilitating four hardware threads (2C4T) per die are active, the maximum CPU frequency achieved is hardware P0.

Consider using CPB when you have applications that can benefit from clock frequency enhancements. Avoid using this feature with latency-sensitive or clock frequency-sensitive applications, or if power draw is a concern. Some workloads do not need to be able to run at the maximum capable core frequency to achieve acceptable levels of performance.

To obtain better power efficiency, there is the option of setting a maximum core boost frequency. This setting does not allow you to set a fixed frequency. It only limits the maximum boost frequency. If the BoostFmax is set to something higher than the boost algorithms allow, the SoC will not go beyond the allowable frequency that the algorithms support.

This setting is accessed as follows:

- System setup:

- System Settings  $\rightarrow$  Operating Modes  $\rightarrow$  Core Performance Boost

- System Settings  $\rightarrow$  Processors  $\rightarrow$  Core Performance Boost

- OneCLI/ASU variable: Processors.CorePerformanceBoost

- Redfish: Processors\_CorePerformanceBoost

Possible values:

Disable

Disables Core Performance Boost so the processor cannot opportunistically increase a set of CPU cores higher than the CPU's rated base clock speed.

Enable (default)

When set to Enable, cores can go to boosted P-states.

#### cTDP (Configurable TDP)

Configurable Thermal Design Power (cTDP) allows you to modify the platform CPU cooling limit. A related setting, Package Power Limit (PPL), discussed in the next section, allows the user to modify the CPU Power Dissipation Limit.

Many platforms will configure cTDP to the maximum supported by the installed CPU. For example, an EPYC 7502 part has a default TDP of 180W but has a cTDP maximum of 200W. Most platforms also configure the PPL to the same value as the cTDP. Please refer to AMD EPYC Processor cTDP Range Table to get maximum cTDP of your installed processor.

If the Determinism slider parameter is set to Performance (see Determinism slider), cTDP and PPL must be set to the same value, otherwise, the user can set PPL to a value lower

than cTDP to reduce system operating power. The CPU will control CPU boost to keep socket power dissipation at or below the specified Package Power Limit.

For maximum performance, set cTDP and PPL to the maximum cTDP value supported by the CPU. For increased energy efficiency, set cTDP and PPL to Auto which sets both parameters to the CPU's default TDP value.

This setting is accessed as follows:

- System setup:

- System Settings  $\rightarrow$  Operating Modes  $\rightarrow$  cTDP

- System Settings  $\rightarrow$  Processors  $\rightarrow$  cTDP

- OneCLI/ASU variable: Processors.cTDP

- Redfish: Processors\_cTDP

Possible values:

- ▶ cTDP

- Auto (default)

Use the platform and the default TDP for the installed processor. cTDP = TDP.

Maximum

Maximum sets the maximum allowed cTDP value for the installed CPU SKU. Maximum could be greater than default TDP. Please refer to Table 9 on page 48 and Table 10 on page 49 for maximum cTDP of each CPU SKU.

– Manual

Set customized configurable TDP

cTDP Manual

Set the configurable TDP (in Watts). If a manual value is entered that is larger than the max value allowed, the value will be internally limited to the maximum allowable value.

#### **PPL (Package Power Limit)**

The parameter sets the CPU package power limit. The maximum value allowed for PPL is the cTDP limit. Set PPL to the cTDP Maximum value when maximum performance is desired. PPL can be set to the cTDP Minimum value or lower but reaching the set value of PPL is not guaranteed when it is set to less than cTDP Minimum.

This setting is accessed as follows:

- System setup:

- System Settings  $\rightarrow$  Operating Modes  $\rightarrow$  Package Power Limit

- System Settings  $\rightarrow$  Processors  $\rightarrow$  Package Power Limit

- OneCLI/ASU variable: Processors.PackagePowerLimit

- Redfish: Processors\_PackagePowerLimit

Possible values:

Auto (default)

Set to maximum value allowed by installed CPU

Maximum

The maximum value allowed for PPL is the cTDP limit.

#### Manual

If a manual value entered that is larger than the maximum value allowed (cTDP Maximum), the value will be internally limited to maximum allowable value.

#### Memory Speed

The memory speed setting determines the frequency at which the installed memory will run. Consider changing the memory speed setting if you are attempting to conserve power, since lowering the clock frequency to the installed memory will reduce overall power consumption of the DIMMs.

With the second-generation AMD EPYC processors, setting the memory speed to 3200 MHz results in higher memory bandwidth when compared to operation at 2933 MHz, but will also result in a higher memory latency. This higher latency is due to the memory bus clock and the memory/IO die clock not being synchronized when the memory speed is set to 3200 MHz. Customers should evaluate both memory speeds for their applications if supported by the second-generation AMD processor.

With the third-generation AMD EPYC processors, setting the memory speed to 3200MHz does not result in higher memory latency when compared to operation at 2933 MHz. The highest memory performance is achieved when the memory speed is set to 3200 MHz and the memory DIMMs are capable of operating at 3200 MHz.

This setting is accessed as follows:

- System setup:

- System Settings  $\rightarrow$  Memory  $\rightarrow$  Memory Speed

- System Information  $\rightarrow$  System Summary  $\rightarrow$  Memory Speed

- OneCLI/ASU variable: Memory.MemorySpeed

- Redfish: Memory\_MemorySpeed

Possible values:

► N

N is the actual maximum supported speed and is auto-calculated based on the CPU SKU, DIMM type, number of DIMMs installed per channel, and the capability of the system. The values in setup show the actual frequency (for example, 3200 MHz, 2933 MHz, 2666 MHz, 2400 MHz).

N-1 (default)

1 speed bin down from maximum speed. If the maximum supported is 3200 MHz, then this "N-1" is 2933 MHz.

► N-2

2 speed bins down from maximum speed

Minimum

The system operates at the rated speed of the slowest DIMM in the system when populated with different speed DIMMs. Installing DIMMs which have a rated speed below 2400 MHz will result in the memory speed getting set to the Minimum value.

Possible Redfish value names are:

- MemorySpeed 3200MHz

- MemorySpeed 2933MHz

- MemorySpeed\_2666MHz

- MemorySpeed\_2400MHz

- ► Minimum

**Tip:** The ThinkSystem SR645 and SR665 servers support memory speed operation at 3200 MHz when the memory is configured with two DIMMs per memory channel and when Performance+ RDIMMs are installed.

Consult the ThinkSystem SR645 and SR665 product guides for more information:

- SR645: https://lenovopress.com/lp1280-thinksystem-sr645-server

- SR665: https://lenovopress.com/lp1269-thinksystem-sr665-server

#### **Memory Interleave**

This setting allows interleaved memory accesses across multiple memory channels in each socket, providing higher memory bandwidth. Interleaving generally improves memory performance so the Auto (default) setting is recommended.

**Note:** This setting is hidden in setup for 2nd Gen EPYC processor, only OneCLI/ASU variable and Redfish attribute are available.

This setting is accessed as follows:

- ► System setup: System Settings → Memory → Interleave

- OneCLI/ASU variable: Memory.Interleave

- Redfish attribute: Memory\_Interleave

Possible values for Memory Interleave:

Auto (default):

Memory interleaving is automatically enabled if DIMM configuration supports it.

Disable

# **Efficiency Mode**

This setting enables an energy efficient mode of operation internal to the AMD EPYC Gen 2 and Gen 3 processors at the expense of performance. The setting should be enabled when energy efficient operation is desired from the processor. If desired, set it to Auto which disables the feature when maximum performance is desired.

This setting is accessed as follows:

- System setup:

- System Settings → Operating Modes → Efficiency Mode

- System Settings  $\rightarrow$  Power  $\rightarrow$  Efficiency Mode

- OneCLI/ASU variable: Power.EfficiencyMode

- Redfish: Power\_EfficiencyMode

Possible values:

Disable

Use performance optimized CCLK DPM settings

Enable (default)

Use power efficiency optimized CCLK DPM settings

# xGMI settings

xGMI (Global Memory Interface) is the Socket SP3 processor socket-to-socket interconnection topology comprised of four x16 links. Each x16 link is comprised of 16 lanes. Each lane is comprised of two unidirectional differential signals.

Since xGMI is the interconnection between processor sockets, these xGMI settings are not applicable for ThinkSystem SR635 and SR635 which are one-socket platforms.

NUMA-unaware workloads may need maximum xGMI bandwidth/speed while other compute efficient NUMA-aware platforms may be able to minimize the xGMI speed and achieve adequate performance with power savings from the lower speed. The xGMI speed can be lowered, lane width can be reduced from x16 to x8 (or x2), or an xGMI link can be disabled if power consumption is too high.

#### 4-Link xGMI Max Speed

The ThinkSystem SR645 and SR665 servers use 4-Link xGMI for maximizing socket-to-socket interconnection performance. Some other vendors' products may use 3-Link xGMI connection to provide 16 more PCIe I/O lanes.

This setting is used to set the xGMI speed. N is the maximum speed and is auto-calculated from the system board capabilities. For NUMA-aware workloads, users can lower the xGMI speed setting to reduce power consumption.

This setting is accessed as follows:

- System setup: